יום בחיי מהנדס תכן לוגי

תואר בהנדסת חשמל זה עולם ומלואו. אנחנו מקבלים בסיס חזק וידע בכל כך הרבה תחומים שונים ומגוונים וכל אחד מאיתנו לוקח את זה למקום אחר בקריירה שלו. בוגר תואר בהנדסת חשמל יכול לבחור לעבוד בתפקידים רבים:

- analog design

- BE engineer

- full chip timing

- emulation

- logic design

- verification

- validation

- post silicon validation

- integration

- clock distribution

- physical design

והרשימה עוד ארוכה.

כולם מאתגרים, כולם מעניינים ולכל אחת מהמשרות הללו מגיעים בוגרי תואר בהנדסת חשמל.

קיימת אינטרקציה רבה בין התפקידים השונים, עליה נרחיב בהמשך המאמר.

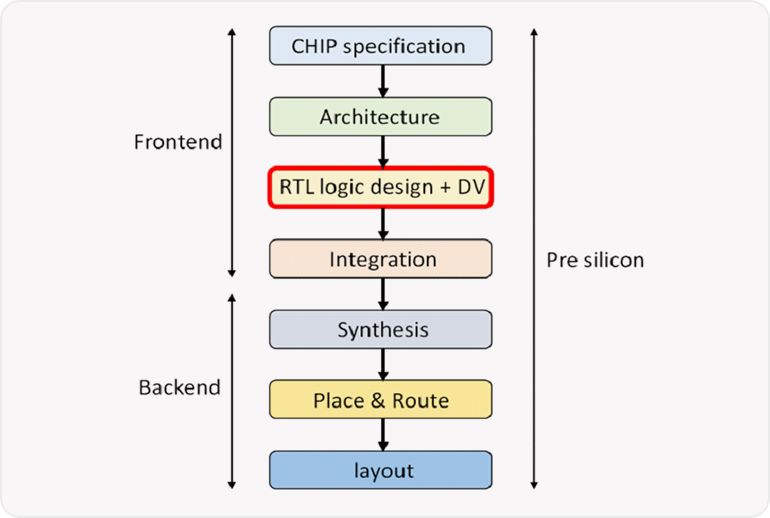

בכל תפקיד האטגרים הם שונים והיכולות הנדרשות שונות ולכן חשוב שנבין מהו כל תפקיד ונבחר עבורנו את מה שהכי מתאים לנו. מהנדס תכן לוגי, logic design engineer, עוסק במימוש הדרישות בקוד חומרה. תהליך הפיתוח של צ'יפים ארוך ומסועף עד שלא ניתן להבין את כל חלקי הפאזל במאמר אחד, לכן נסתפק כאן בתהליך הזרימה הבא:

ניתן לומר שהארכיטקט מגדיר את ה- "מה" כלומר מה כל בלוק בצ'יפ צריך לבצע. מהנדס התכן לוגי, ה- logic design engineer או ה-frontend engineer, כולם שמות נרדפים, מגדיר את ה-"איך" כלומר איך לבצע את הדרישה, תוך שהוא נותן את הדעת על איך כל החלטה שלו משפיעה ישירות על המימוש החומרתי.

נבין זאת דרך הדוגמא הבאה:

נניח שאנחנו בחברה שעוסקת בפיתוח chip לעיבוד תמונה והארכיטקט מגדיר שהבלוק הראשון בצ'יפ, כלומר הבלוק שמקבל את התמונות ישירות מה-sensor, צריך להיות מסוגל לקלוט 30 תמונות בשניה כאשר כל תמונה היא ברזולוציה של 19201080X .

הארכיטקט יעביר למהנדס התכן לוגי מסמך שמתאר את דרישת הארכיטקטורה הנ"ל. למהנדס התכן לוגי קיים חופש רב בבחירת הפתרון וצורת המימוש.

- תחילה יש להחליט יחד עם ארכיטקט השעונים, באיזה תדר הבלוק יעבוד. ככל שתדר השעון מהיר יותר כך החומרה תספיק לבצע פעולות רבות יותר אך נשלם על זה בצריכת הספק גבוהה. תמיד נעדיף לעבוד בתדר השעון המינימלי שעדיין מספיק לנו לצורך ביצוע הדרישה. בהינתן כמות המידע שיש לעבד ורוחב ה-data שמגיע בכל מחזור שעון ניתן לקבוע את התדר.

- לאחר מכן מהנדס התכן לוגי יחליט האם לשמור את המידע בזכרון פנימי בתוך הצ'יפ, זהו ה- RAM, אך אם המידע גדול מידי נאלץ להשתמש בזיכרון חיצוני, DDR, ונשלם ב-latency גבוה.

- מהנדס התכן לוגי יממש המרת פרוטוקלים בעזרת FSM בין הצורה בה המידע מגיע מהסנסור לבין הצורה בה הזיכרון מצפה לקבל אותו.

- מהנדס התכן לוגי ישאף להכניס בקוד אמצעים ל-debug באמצעותם יבדוק את תקינות הבלוק לאחר הייצור.

- לאחר שמהנדס התכן לוגי בחר את צורת המימוש הוא יעבור לשלב כתיבת הקוד ויתאר את הפתרון בחומרה. השפות לתיאור חומרה הן Verilog או VHDL.

מהנדס הוריפיקציה, Design Verification, או בקיצור DV, גם הוא מקבל את מסמך הארכיטקטורה שקיבל מהנדס התכן לוגי, ומפתח בלוקים שמדמים את התנהגות הסנסור ואת התנהגות הבלוק הבא בשרשרת. כך מהנדס הוריפיקציה יוצר סימולציה דרכה אפשר לבחון את תקינות הבלוק שמימש מהנדס התכן לוגי.

לאחר שהבלוק מומש וכל הבדיקות עברו בהצלחה, יעביר מהנדס התכן לוגי את הקוד שלו למהנדס האינטגרציה על מנת שיחבר את הבלוק יחד עם שאר הבלוקים בצ'יפ. אנשי ה-backend יקבלו את כל הקוד של כל הצ'יפ יחד (או איזור גדולים ממנו) ויחלו בתהליך הסינטזה. אנשי ה-backend יצרו קשר עם מהנדס התכן לוגי במקרים בהם הבלוק שלו, יחד עם בלוקים אחרים בצ'יפ, יוצר בעיית timing שדורשת שינוי RTL.

אם כן, ראינו שלמהנדס התכן לוגי ממשקי עבודה רבים עם הקבוצות השונות בחברה – איש הוריפיקציה, הארכיטקטים השונים, האינטגרטור ואנשי ה-backend.

מה הופך מהנדס תכן לוגי למעולה בתחומו?

מהנדס תכן לוגי נמצא תמיד בצמתים מכרזיים בפיתוח, הוא חוליה שמקשרת בין צוותים רבים ודיסציפלינות שונות. חשוב מאוד שהוא יהיה פדנט כך שהקוד שיכתוב יממש את הדרישות בצורה מדויקת. בנוסף הוא צריך להיות "ראש גדול", למשל כשיש שינוי בארכיטקטורה שגורר גם שינויים בבלוק שלו, עליו לבצע פעולות רבות:

- לתקן את הקוד, לעדכן את המסמכים, לוודא שהוריפיקטור מעדכן את הטסט בהתאם, לתת תיקון לאינטגרטור, ואם זה שלב מתקדם בפרויקט אז גם יש צורך לעדכן את אנשי ה-BE מראש.

- הקטנת ראש ותיקון הקוד בלבד, מבלי לוודא שכל שאר הצוותים שמסביב נרתמים לשינוי, יגרום לבאגים חדשים לצוץ בהמשך.

מהנדס תכן לוגי מכיר את הדקויות בקוד שיכולות להוות בעיה בשלב מאוחר יותר בסינטזה. לעיתים יש יותר מדרך אחת לממש את הדרישה והצורה בה הקוד נכתבת מגדירה את המעגל שימומש. ככל שהמהנדס יהיה מנוסה יותר כך ידע בדיוק איזו חומרה תמומש עבור איזה קוד. בצורה כזאת הוא ימנע באגים שעתידיים להתגלות רק בשלבים מאוחרים בתהליך הפיתוח.

עד כאן טעימה על קצה המזלג מעבודתו של איש התכן לוגי, logic design engineer